ibis系统,揭秘高速数字电路仿真与信号完整性分析的关键工具

时间:2024-11-22 来源:网络 人气:

IBIS系统:揭秘高速数字电路仿真与信号完整性分析的关键工具

随着电子技术的飞速发展,高速数字电路设计在各个领域得到了广泛应用。然而,高速数字电路设计面临着信号完整性(Signal Integrity, SI)和时序(Timing)等一系列挑战。为了确保电路设计的成功,工程师们需要借助专业的仿真工具来分析和优化电路性能。IBIS系统作为其中一款重要的工具,在高速数字电路仿真与信号完整性分析中发挥着关键作用。

IBIS(I/O Buffer Information Specification)是一种公开的、基于行业标准的数字电路输入输出建模规范。它通过描述芯片I/O缓冲器的电气特性,帮助工程师在电路设计阶段预测和分析信号完整性问题。IBIS模型使用ASCII文本文件格式,提供表格化的电压-电流(V/I)和电压-时间(V/T)信息,不包含专有数据,如晶体管尺寸、缓冲器原理图设计中使用的器件模型参数和电路等。

与传统的SPICE模型相比,IBIS系统具有以下优势:

仿真速度快:IBIS模型不包含详细的晶体管结构和工艺技术,因此仿真速度更快,适用于高速数字电路设计。

易于获取:芯片厂商可以轻松地提供IBIS模型,而不必透露知识产权。

通用性强:IBIS模型不依赖于特定的仿真工具,可以在大多数行业级平台中运行。

易于使用:IBIS模型使用ASCII文本文件格式,方便工程师进行编辑和修改。

IBIS系统在以下场景中发挥着重要作用:

高速数字电路设计:在电路设计阶段,使用IBIS系统进行信号完整性分析和时序分析,确保电路性能满足设计要求。

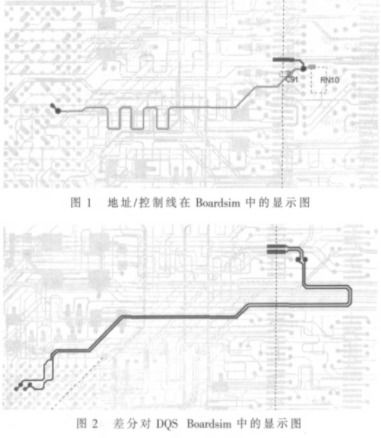

PCB设计:在PCB设计阶段,使用IBIS系统进行信号完整性仿真,优化PCB布局和布线,降低信号完整性问题。

芯片封装设计:在芯片封装设计阶段,使用IBIS系统分析封装对信号完整性的影响,优化封装设计。

系统级仿真:在系统级仿真阶段,使用IBIS系统分析整个系统的信号完整性,确保系统性能满足设计要求。

IBIS系统的实现方法主要包括以下步骤:

获取IBIS模型:从芯片厂商或第三方数据库获取所需的IBIS模型。

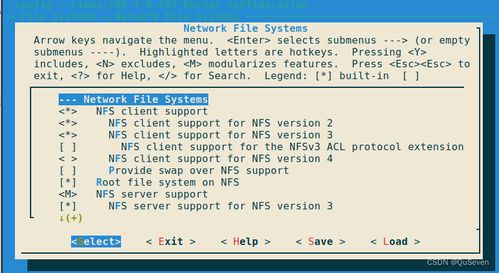

建立仿真环境:选择合适的仿真工具,如Hyperlynx、ADS等,并建立仿真环境。

设置仿真参数:根据实际电路设计,设置仿真参数,如信号频率、传输线长度、阻抗等。

运行仿真:运行仿真,分析信号完整性问题,如串扰、反射、过冲等。

优化设计:根据仿真结果,对电路设计进行优化,降低信号完整性问题。

IBIS系统作为一款重要的仿真工具,在高速数字电路设计领域发挥着关键作用。通过使用IBIS系统,工程师可以提前预测和分析信号完整性问题,优化电路设计,提高电路性能。随着电子技术的不断发展,IBIS系统将在未来发挥更加重要的作用。

相关推荐

教程资讯

教程资讯排行